## COMPARATIVE ANALYSIS OF 4-BIT AND 8-BIT REVERSIBLE ARITHMETIC LOGIC UNIT (RALU) BASED ON REVERSIBLE GATE

Kundan Kumar, M-Tech Scholar, Rabindranath TAGORE University, Bhopal kundan13647@gmail.com, Amrish Kumar Singh, Assistant Professor, Rabindranath TAGORE University, Bhopal amrishkumarsingh92@gmail.com

Abstract— With the advent of nanotechnology, transistors are getting smaller and growing in number according to Moore's Law. Reversible or information-lossless circuits have applications in digital signal processing, communication, computer graphics and cryptography. Reversibility plays an important role when energy efficient computations are considered. Reversible logic is used to reduce the power dissipation that occurs in classical circuits by preventing the loss of information. This paper comparative study is reversible design for 4-bit, 8-bit ALU. These ALU consists of different types of operations i.e. arithmetic and logical operations. The include addition, arithmetic operations subtraction, multiplication, division and the logical operations include NAND, AND, OR, NOT, XNOR, NOR and XOR. All the modules are being designed using the basic reversible gates. Simulation and verification of the design will perform using Xilinx 14.1i with different device family. In this paper, we have considered an 4-bit and 8-bit arithmetic logic unit (ALU) for implementation using RL gates and analyzed its performance for power dissipation and propagation delay.

Keywords—Component, formatting, style, styling, insert

### **I. INTRODUCTION**

The technological advancements have made integration of billions of transistors on single die possible which has given the designers, the flexibility and freedom of putting more and more functionality on the same die. With this, the issue of heat dissipation is becoming of greater concern to researchers as the transistor heat dissipation reaches the Landauer limit. Reversible logic is predicted to be an alternative to conventional computing due to lesser energy dissipation and exponentially faster problem-solving capacity This has resulted in increased power consumption and has opened plethora of techniques dealing with it. Power dissipation in the electronic system is a very crucial limiting factor that can be reduced or minimized with the help of using reversible logic (RL) circuits. RL is emerging as an important research area in the recent years due to its ability to reduce the power dissipation, which is the main requirement in low-power digital system design. Energy dissipation is proportional to the number of bits lost during computation. The reversible circuits do not lose information bits and can generate unique outputs from specified inputs and vice versa. In modern very large scale integration (VLSI) systems, the power dissipation is high due to rapid switching of internal signals. Also, the systems designed using conventional circuits dissipate heat due to the loss of information bits during computation. Landauer <sup>[1]</sup> showed that the loss of every bit of information results in dissipation of KT\*ln2 J of heat energy, where K is Boltzmann constant and T is temperature at which the operation is performed. Bennett  $^{[2]}$  showed that the heat dissipation due to loss of information bits can be avoided

when the circuit is designed using RL circuits. A gate is considered reversible only if every input has a unique output assignment. Hence, there is a one-to-one mapping between the input and output vectors, i.e., it has same number of inputs and outputs  $^{[2]-[4]}$ . The RL structures can be realized in the quantum logic system with minimum number of cells <sup>[5]</sup>. The complexity analysis of the ancilla bits can also be made with shortest path formulation and integer linear program (ming) (ILP) formulation for the RL <sup>[6]</sup>. An implementation of adder/subtractor and multiplier circuits using RL gates was done and its performance was analyzed. The paper is follows: organized as In Section 2, basic RL gates and their function are discussed. The various elements of ALU using the reversible gates are presented in Section 3. The simulated results of the various components of ALU are discussed in Section 4. In Section 5, performance of the various blocks is compared with the existing ones. Finally, conclusions are given in Section 6

### **II. REVERSIBLE GATES**

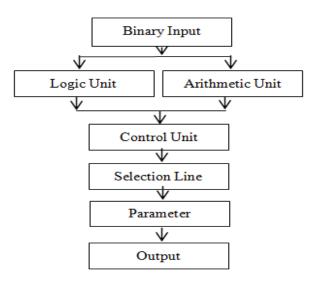

A reversible logic gate is an n-input n-output logic device with one-to-one mapping. This helps to determine the outputs from the inputs and also the inputs can be uniquely recovered from the outputs. ALU stands for "Arithmetic Logic Unit." An ALU is an integrated circuit within a CPU or GPU that performs arithmetic and logic operations. Arithmetic instructions include addition, subtraction, and shifting operations, while logic instructions include Boolean comparisons, such as AND, OR, XOR, and NOT operations.

**Definition 1:** A reversible gate is a n x n circuit (n inputs, n s outputs) which uniquely maps each of its input to its corresponding output <sup>[3]</sup>. So, a reversible gate must satisfy the following conditions-

It should have equal number of inputs and outputs.

It should have one to one mapping between its inputs and outputs.

3) There should be neither feedback nor fanout in case of a reversible gate.

The above conditions ensure that the circuit designed using reversible gates does not lose any information bits as the inputs are processed by it and thus, the circuit is reversible. Such a circuit can overcome the energy efficiency barrier imposed by Landauer <sup>[1]</sup>. Maintaining the Integrity of the Specifications.

**Definition 2:** Ancilla inputs of a reversible gate are the inputs which should be maintained constant at either logic '0' or logic '1' so that the gate realizes the required Boolean function<sup>[3]</sup>.

**Definition 3:** Garbage outputs of a reversible gate are the extra outputs which are of no logical use and are present only to maintain reversibility <sup>[3].</sup>

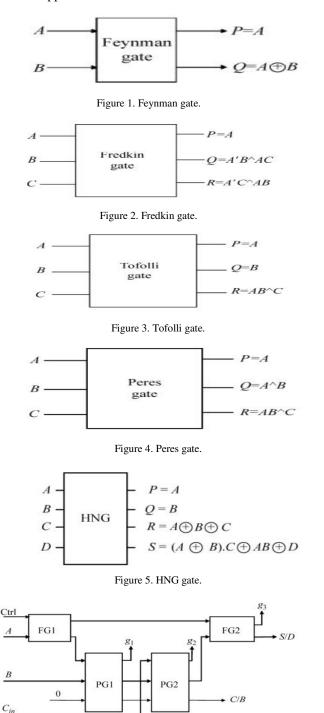

Reversible gates are bijective. There exist many reversible gates in the literatures <sup>[3], [4], [8], [9].</sup> Among them 2\*2 Feynman gate [8], 3\*3 Fredkin gate [3], 3\*3 Toffoli gate (TG) [4], 3\*3 Peres gate (PG) [9], new gate (NG) [10] and 4\*4 HNG gate [11] are the gates utilized to construct the reversible applications.

Figure 6. Reversible design of full adder/subtractor.

### III. LITERATURE SURVEY

The research on reversible logic is expanding towards both design and synthesis. Several researchers have been exploring techniques for synthesis of reversible logic circuits and many interesting contributions have been made. The synthesis of reversible circuits that employ a minimum number of gates and contain no redundant input output line-pairs (temporary storage channels) is investigated in; Researchers in have used the positive-polarity Reed-Muller expansion of a reversible function to synthesize the function as a network of Toffoli gates; The work in has illustrated the number of garbage outputs that must be added to a multiple output function to make it reversible<sup>[1]</sup>.

The research on reversible logic is expanding towards both design and synthesis. The synthesis of reversible circuits that employ a minimum number of gates and contain no redundant input-output line-pairs (temporary storage channels) is investigated in; Researchers in have used the

Positive-polarity Reed-Muller expansion of a reversible function to synthesize the function as a network of Toffoli gates; The work in has illustrated the number of garbage outputs that must be added to a multiple output function to make it reversible.

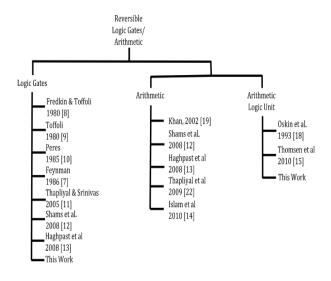

Figure7. Taxonomy of Relevant Works

Further a new reversible design method that uses the minimum number of garbage outputs is also proposed; the authors in investigate the problem of optimally synthesizing 4-bit reversible circuits using an enhanced bi-directional synthesis approach. Thus, in synthesis of reversible logic circuits, the optimization in terms of number of ancilla input bits and also the delay are not yet addressed except in the recent work which discusses about the post synthesis method for reducing the number of lines (qubits) in the reversible circuits<sup>[5]</sup>.

The design of reversible sequential circuits was first introduced in 1988, in which the design of the JK latch was discussed. Later, the design of the RS latch was introduced

#### INTERNATIONAL JOURNAL OF RESEARCH IN TECHNOLOGY AND MANAGEMENT (IJRTM) ISSN 2454-6240

in. The design uses two cross-coupled reversible NOR gates as used in conventional logic for designing the RS latch. The design was clock less in nature, i.e., there was no enable signal. The NOR gates were designed from the reversible Fredkin gate. The work was limited to the design of RS latch only. In the authors introduced reversible latches such as D latch, T latch, etc., along with their corresponding flip-flops. The flip-flops were designed using master-slave strategy in which one reversible latch works as a master latch and the other works as a slave latch <sup>[6]</sup>.

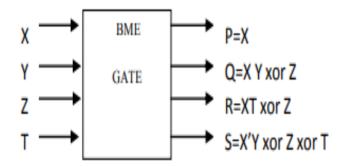

Figure 8. Block Diagram of BME Gate

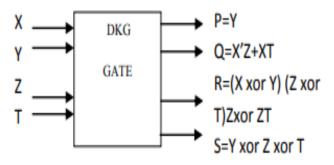

Figure 9. Block Diagram of DKG Gate

The classical computational process which is irreversible, onebit of information is lost for each logical operation carried out by it. But in 1961, Rolf Landauer's principle states that for each bit of information. However, this loss of energy is legible for simple circuits and become significant for complex circuits. In 1973, Bennet showed that there would be no energy dissipation if computations are done in the reversible way <sup>[2].</sup> Resultantly, a new paradigm in circuit design evolved with the aim of reducing the entropy increase and energy dissipation <sup>[3].</sup>

Table 1: Summary of Literature Review

| Title                                                                                         | Methodology                                                      | Parameter                                      | Scope                  |

|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------|------------------------|

| Design and<br>Optimization of 8 bit<br>ALU using<br>Reversible<br>Logic                       | Design 8-bit<br>reversible ALU<br>using COG and<br>HNG Gate      | Quantum<br>cost = 26,<br>garbage<br>output = 9 | Low power<br>computing |

| Design and<br>Implementation of<br>Optimized 32-Bit<br>Reversible<br>Arithmetic Logic<br>Unit | Design 32-bit<br>reversible<br>ALU using<br>PFAG and HNG<br>Gate | Quantum<br>cost = 28,<br>ancilla<br>input = 12 | CMOS technology        |

|                       |                   |            | www.ijrtm.com   |

|-----------------------|-------------------|------------|-----------------|

| Design and Synthesis  | Design 16-bit     | Gate       | Low area        |

| of Reversible         | reversible ALU    | count =27  | consumption     |

| Arithmetic and        | using TSG and     | Delay =    |                 |

| Logic Unit (ALU)      | HNG Gate          | 12.64      |                 |

| Design of a           | Design 4-bit      | Cost =24   | Less Complexity |

| Reversible ALU        | reversible ALU    | Delay =    |                 |

| based on Novel        | using Toffoli and | 11         |                 |

| Programmable          | HNG Gate          |            |                 |

| Reversible            |                   |            |                 |

| Logic Gate Structures |                   |            |                 |

| Design of Speed,      | Design 1-bit      | Number     | Low area and    |

| Energy and Power      | reversible ALU    | 17.4 ns    | power           |

| Efficient Reversible  | using Peres and   |            |                 |

| Logic Based Vedic     | HNG Gate          |            |                 |

| ALU for               |                   |            |                 |

| Digital Processors    |                   |            |                 |

| Arithmetic & Logic    | Design 8-bit      | Quantum    | Nano technology |

| Unit (ALU) Design     | reversible ALU    | cost= 34,  |                 |

| using Reversible      | using PFAG and    | garbage    |                 |

| Control Unit          | HNG Gate          | output     |                 |

|                       |                   | =14        |                 |

| Design and Analysis   | Design 16-bit     | Gate count | Digital Circuit |

| of 16 Bit Reversible  | reversible ALU    | ancilla    | system          |

| ALU                   | using HNG and     | input =12  |                 |

|                       | PAOG Gate         | _          |                 |

| Design of a           | Design 1-bit      | Delay =    | Digital Signal  |

| Reversible ALU        | reversible ALU    | 18.3 ns,   | Processing      |

| Based on Novel        | using DPG and     | slice      |                 |

| Programmable          | TOG Gate          | =45,       |                 |

| Reversible Logic      |                   | LUTs =     |                 |

| Gate Structures       |                   | 36         |                 |

Further, such a logical structure must possess the same number of inputs and outputs and a one-to-one mapping between the input and output states. Any device designed according to the above constraints is known as a reversible logic device <sup>[4].</sup> Reversibility becomes an essential parameter for the future computer designs <sup>[4]</sup>. Reversible gates or circuits allow the reconstruction of the inputs from the observed outputs. Reversible logic is applicable to the research areas such as low power CMOS design, optical computing, bioinformatics, computing, quantum thermodynamic technology, DNA computing and nanotechnology<sup>[4]</sup>. A reversible circuit should be designed using minimum number of reversible logic gates.

Quantum technology is essentially reversible and is one of the important promising technologies for future computing systems. In addition to reversibility, it has unique features such as quantum superposition, quantum parallelism and quantum entanglement that allows for solving problems much more powerfully than in classical computing. (Observe that the quantum circuit is reversible when it calculates in Hilbert Space before the measurement. It is no longer reversible after measurement, since the probabilistic measurement cannot be reversed). Although only a few quantum algorithms are known in 2010, many problems can be reduced to some of these algorithms, for instance to the Quantum Fast Fourier Transform or to Grover's algorithm. Thus, any NP-hard problem can be reduced to Grover's algorithm to give a practically useful and substantial reduction in complexity for large values of N. This reduction is, however, not as high as in the case of the exponential speedup obtained by the famous Shor's quantum algorithm for integer factorization.

# IV. REVERSIBLE ADDER DESIGNS AND COMPARISON

## A. Design of Reversible Ripple-Carry and Carry-Select Adders

In order to design the most efficient 32-bit reversible arithmetic logic unit, we designed and compared reversible implementation of ripple-carry, carry-select and carry look- ahead adders. A reversible ripple-carry adder and a reversible carry-select adder are designed using the new ALU. The ripple-carry adder has a cost of 40n-3 and a delay of 4n + 13. The most-significant bit of the ALU ties the Sum output to the SLT i/p of the least significant bit, and the SLT input for all other bits is 0. The reversible carry-select adder uses the carry out of the first n/2 bits as the control signal to a Fredkin gate implemented as a multiplexer, since the next n/2 bits are calculated with both a carry-in of 0 and a carry-in of 1, which requires a cost of 40(3n/2)-3 and a delay of 2n + 19.

#### B. Reversible Kogge-Stone Cumulate Logic

Next, a reversible carry look-ahead adder based on the Kogge-Stone adder is presented <sup>[9]</sup>. First, a RKS Cumulate utilized in the calculation of the carry out signal is designed and verified. The cost of the RKSC is 14 and it has a worst-case delay of 4. A cost and delay analysis of the presented adders in the ALU implementation is presented in Table 2.

The ripple-carry adder has the lowest cost, but the highest delay. The carry look-ahead adder has a prohibitively-high cost, but the most-desirable delay.

Table 2: Cost and delay comparison of 4-bit reversible adders.

|       | Ripple-Carry | Carry-Select | Kogge-Stone |

|-------|--------------|--------------|-------------|

| Cost  | 192          | 293          | 2287        |

| Delay | 128          | 83           | 25          |

C. Comparison of Reversible Ripple-Carry and Carry-Select Adders with Sparsity

The Kogge-Stone adder may be enhanced to reduce overhead and design complexity by generating a carry every *n*-bits instead of every bit, and the carry is used for the carry- in of an n-bit ripple-carry or carry-select adder. The number *n* is defined as sparsity. This implementation was designed and tested for sparsity-4, 8 and 16 with the corresponding n- bit ripple-carry and carry-select adders. The cost and delay comparison of each implementation is shown in Table 5. The design for each adder presented in Table 5 was verified using VHDL in Xilinx 12.4.

Table 3 : Cost and delay comparison of modified carry look-ahead implementations for 8-bit reversible adders

|              | Sparsity-4 | Sparsity-8 | Sparsity-16 |

|--------------|------------|------------|-------------|

| Ripple-Carry | Cost: 666  | Cost: 462  | Cost: 316   |

|              | Delay: 40  | Delay: 56  | Delay: 88   |

| Carry-Select | Cost: 802  | Cost: 578  | Cost: 422   |

|              | Delay: 37  | Delay: 45  | Delay: 61   |

## V. PROPOSED METHODOLOGY AND RESULT DISSCUSSION

The RALU utilizes the DKG gate and BME gate to produce eight logical calculations: transfer A, addition, Sub, XOR, OR, AND, NOT and NAND. The cost and delay calculations are identical to the ALU in figure 10. The RALU has 8 inputs and 8 outputs. The inputs consist of three data inputs (A, B and Cin) and five (S0, S1, S2, S3, S4) lines.

Figure 10: Flow of bit Slice ALU

The proposed implementation is programmed (Described) and implemented using VHDL language which is a Hardware Description Language that was developed by the Institute of Electrical and Electronic Engineers (IEEE) as a standard language for describing the structure and behavior of digital electronic systems. It has many features appropriate for describing the behavior of electronic components ranging from simple logic gates to complete microprocessors and custom chips. The resulting VHDL simulation models can then be used as building blocks in larger circuits (using schematics, block diagrams, or system-level VHDL descriptions) for the purpose of simulation.

1. Design 4-bit and 8-bit using different types of reversible gate.

2. Design different types of programmable reversible gate and compared.

3. Design free garbage based architecture using different types of input and compared existing algorithm. Hand calculation of delay and area in reversible arithmetic logic unit in different inputs. All the modules design to different device family i.e. Spartan-3, Virtex-4 and Virtex-7.

### VI. CONCLUSION

The 4-bit reversible ALU is designed by integrating various sub modules that includes adder/subtract or, and logical unit. The logical unit performs AND, OR, NOR, XOR, NAND. The performance evaluation of the various sub modules are carried out using Modalism 6.5 tools and it was found that the circuits designed using reversible logic showed reduced delay and power. As a future work more arithmetic and logical function can be used. RL circuit is an emerging technology with promising applications because of its low-power dissipation. In this paper, a novel architecture of a reversible 8-bit ALU has been proposed and it is implemented in circuit level. Each block of the ALU was designed using the basic reversible gates. The simulation and synthesized result shows that RL-based design dissipates less power up to maximum of 39% improvement and 10% improvement in the delay. Thus the reversible ALU structure is suitable for portable low-power applications. In future, this design can be extended to 16, 32 and 64 bits. A reversible divider can also be designed and included into this ALU. Moreover, this design may be extended to gate level implementation.

### REFERENCES

- M. Morrison and N. Ranganathan, "Design of a Reversible ALU Based on Novel Programmable Reversible Logic Gate Structures," IEEE International Symposium on VLSI, 2011, pp. 126-131.)

- [2] R. Landauer, "Irreversibility and Heat Generation in the Computational Process," IBM Journal of Research and Development, vol. 5, 1961, pp. 183-91..

- [3] A. Peres, "Reversible Logic and Quantum Computers," Physical Review, vol. 32, iss. 6, 1985, pp. 3266-3267.

- [4] ShefaliMamataj, Biswajit Das, Anurima Rahaman, An Optimized Realization of ALU for 12-Operations by using a Control Unit of reversible gates, International Journal of Advanced Research in Computer Science and Software Engineering, Volume 4, Issue 1, ISSN: 2277 128X, January 2014.

- [5] International Conference on Nanotechnology, 2011

- [6] M. Morrison, M. Lewandowski, R. Meana and N. Ranganathan, "Design of Static and Dynamic RAM Arrays Using a Novel Reversible Logic Gate and Decoder," To Appear in the IEEE 11th

- [7] Matthew Morrison and Nagarajan Ranganathan, "Design of a Reversible ALU based on Novel Programmable Reversible Logic Gate Structures", 2013 IEEE Computer Society Annual Symposium on VLSI.

- [8] Lekshmi Viswanath and Ponni.M, "Design and Analysis of 16 Bit Reversible ALU", ISSN: 2278-0661 Volume 1, Issue 1 (May-June 2012), PP 46-53.

- [9] C.H. Bennett, "Logical Reversibility of Computation", IBM Research and Development, pp. 525-532, November 1973.

- [10] M. Haghparast, S. J. Jassbi, K. Navi and O. Hashemipour, "Design of a Novel Reversible Multiplier Circuit using HNG Gate in Nanotechnology", World Applied Sci. J., Vol. 3, 2008, pp. 974-978

- [11] P. Kogge and H. Stone, "A Parallel Algorithm for the Efficient Solution of a General Class of Recurrence Equations," IEEE Transactions on Computers, vol. C-22, iss. 8, 1973, pp. 786-793.

- [12] H. Thapliyal and N. Ranganathan, "Testable Reversible Latches for Molecular QCA," IEEE Conference on Nanotechnology, 2008, pp. 699-702

- [13] H. Thapliyal and N. Ranganathan, "Design of Reversible Sequential Circuits Optimizing Quantum Cost, Delay, and Garbage Outputs," ACM Journal on Emerging Technologies in Computing Systems, 2010.